|

8.1. Les processeurs, comment ça fonctionne à l'intérieur |

| 1. Notions de base | 2. Techniques d'atelier | 3. Configuration des réseaux | 4. Dépannages spécifiques |

| Accueil | Contacts | Plan du site |

Sans rentrer trop dans les détails, nous allons expliquer le fonctionnement interne des processeurs informatiques actuels: juste les grosses lignes pour comprendre l'utilisation des bus internes (dual Core, ...), l'utilisation des caches, les processeurs RISC et CISC (surtout le passage de l'un à l'autre). Comprendre l'architecture interne des microprocesseurs actels.

1. Un petit historique pour comprendre l'évolution.

Le premier X86 compatible date de 1981 et est implanté dans les premiers XT d'IBM: c'est le 8088. C'est un simple processeur 16 bits de l'époque avec une architecture interne de type CISC. Pour comprendre le terme CISC (Complex Instruction SET Computer), il faut faire un retour dans les considérations commerciales des premiers fabricants de processeurs. A l'époque, la vitesse n'était pas forcément le but ultime, on est aux balbutiements et tout se programme quasiment en assembleur (un langage de programmation machine constitué de lignes de codes écrits en hexadécimal, aidé par quelques compilateurs qui transposent des lignes de code en texte en instructions machines-assembleur). Les fabricants vont intégrer des instructions simples mais aussi des instructions nettement plus complexes. Ceci permet d'écrire quelques lignes de codes pour faire exécuter des fonctions complexes, et c'est une des base du marketing de l'époque, nos programmes s'écrivent plus vite avec moins d'instructions ... Pourtant, ces commandes sont écrites (leur code en hexadécimal - binaire) d'une manière plutôt anarchiste ce qui oblige un décodage interne complexe. En plus, la majorité de ces instructions spécifiques ne sont pas utilisées car méconnues par les programmeurs de l'époque. C'est la base du CISC, une longue liste d'instructions complexes mais qui sont peu utilisées en pratique et qui ralentissent finalement le fonctionnement du processeur. Les processeurs suivant sont compatibles avec les instructions de ces "vieux" 8088, donc doivent pouvoir lire ces commandes.

Nexgen, firme aujourd'hui disparue, va

modifier cette pratique en utilisant un décodeur. L'idée est d'arriver

avec des instructions 8088, de les prédécodées puis de les faire

passer dans un processeur qui connaît moins d'instruction mais les

exécute directement et nettement plus rapidement, c'est l'architecture RISC (Reduce Instructions Set Computer,

nombre d'instructions réduites). Cette solution est adaptée ensuite

par Intel depuis les Pentium II et par AMD depuis les K6-2.

Au total, le résultat est le même mais le coeur du processeur va exécuter l'ensemble plus vite, d'où un gain de temps et de performance.

2. Le fonctionnement des mémoires cache.

Dans

les premiers processeurs, sa vitesse externe était lié à celle de la

RAM. Ca a marché jusqu'aux 486 mais les vitesses des mémoires ont

montré leur limitations par rapport à celle des processeurs, ce qui

explique (à l'époque) les 486 X2. Du coup, le processeur tourne plus

vite que la mémoire et les données - programmes n'arrivent plus assez

vite pour satisfaire la gourmandise des parties internes.

La première idée a été de mettre un circuit entre la Ram et le processeur qui récupère les instructions et données qui sembles passer les plus souvent pour les mettre dans une mémoire intermédiaire plus rapide mais plus chère (c'est le cache L2). Pourtant ce circuit n'a aucune intelligence et ne sait pas ce qui se passe. Un exemple standard: un monsieur passe devant vous 4 X en cinq minutes ne prouve pas qu'il passe souvent, il est peut-être juste perdu. Pourtant, cette solution procure des hausses importances de performances (à l'époque jusque 30 % de performances en plus quand même ...). Là aussi les premiers Pentium II et consort vont modifier le fonctionnement par rapport aux 386 et 486, le contrôleur est directement le processeur et implanté avant le décodage.

Pourtant, des parties de programmes et

données sont

nettement plus utilisées que d'autres. Revenons à notre processeur

CISC ci-dessus. Il va simplement récupérer les données les plus

utilisées dans une mémoire interne en fin de traitement pour les

renvoyer à la demande à l'unité de décodage. Pour les codes de

programmes, c'est encore plus simple, il va les mettre directement en

"cache"après l'unité décodage (donc prédécodées). La

taille du cache L1 est typiquement de 64 K pour chaque partie (soit 128

K octets au total).

Reste les premières versions du cache L2 (géré par un circuit extérieur). Quelques cartes mères (mais aussi processeurs vont utiliser un cache L2 géré par le processeur et par ... un circuit externe. Du coup, celui géré par un circuit externe va devenir .... L3 mais aussi servir pour le partage interne dans les multi-cores actuels.

3. Les avantages actuel de l'architecture RISC

Reprenons cette exécutions d'instructions simples mais prédécodées. Dans un "ancien processeur", chaque instruction est décodée à tour de rôle, quelque soit sont type (calculs sur des nombres entiers, réels, déplacement de données en mémoire, ....). C'est là l'avantage du RISC dans les processeurs actuels, mettre plusieurs sous parties spécialisées pour leur taches respectives qui peuvent travailler simultanément (du moins s'ils reçoivent des instructions pour travailler, d'où l'intérêt des mémoires caches).

Reprenons notre partie interne avec la partie exécution simple d'instructions et ... dissocions les parties en fonction de leurs tâches respectives en prenant un exemple plus commun. J'arrive dans un restaurant, la personne de l'accueil va placer les gens à table, un premier serveur va commander l'apéritif, un deuxième va prendre la commande, un autre va livrer les plats, ... Ca va aller tout de suite plus vite, chaque membre du personnel va d'abord être plus spécialisé mais aussi ne pas faire 30 choses à la fois. C'est le même principe pour un processeur actuel. On pourrait faire mieux? Et oui, on va augmenter le nombre de personnes spécialisées. C'est le principe actuel dans le coeur des processeurs, mettre plusieurs unités qui font le même travail en même temps si c'est nécessaire, ce qui n'est pas possible avec une architecture CISC. L'hyperthreading implanté dans les derniers Pentium IV (pas tous) et dans l'I7 utilisent finalement cette idée en découpant les programmes en parties distinctes qui sont exécutées par des parties différentes du processeur. Il intègre juste un mécanisme pour suivre chaque morceau (en gros, il est capable de mémoriser deux adresses mémoires en même temps).

4. Et maintenant, l'intégration dans les multi- coeurs.

D'abord, une carte mère avec deux processeurs ou un seul dual core? Un multi-coeur est intégré dans le même circuit et utilise un seul socket. Par contre, deux processeurs distincts utilisent chacun leur propre socket. De fait, les bus externes sont partagés dans un processeur multi-core alors qu'ils sont multiplexé via un chipset spécialisé sur une carte mère utilisant deux processeurs (ou plus). Les accès mémoires et périphériques sont donc plus rapides. De fait, les performances globales sont légèrement supérieures pour deux processeurs par rapport à un Dual-Core. Mais ... Les deux coeurs d'un Dual Core sont mieux liés pour partager des données et instructions. Ils communiquent directement entre-eux sans passer par un circuit intermédiaire.

Comment se font les transferts de données à l'intérieur d'un multi-coeur? Ca dépend du type de processeur.

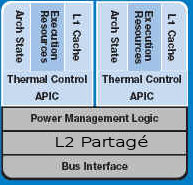

Dans

les Core deux Duo Intel (et quadri), les deux processeurs sont

collés ensemble via le cache L2 qui permet le partage, ensuite à un

bus externe (qui varie suivant les modèles) comme ci-contre.

Dans

les Core deux Duo Intel (et quadri), les deux processeurs sont

collés ensemble via le cache L2 qui permet le partage, ensuite à un

bus externe (qui varie suivant les modèles) comme ci-contre.

Les derniers processeurs gèrent directement la Ram, sans passer par un circuit intermédiaire (appelé le Northbridge).

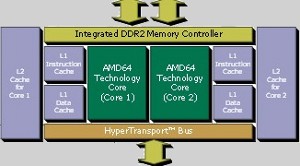

AMD

avec les Athlon X2 et autres Opteron utilise une autre technique, celle

de l'utilisation d'un bus interne qui sert aussi de bus externe (c'est

l'hyper-transport). Dans ce cas, le bus interne sert non seulement à

raccorder les différents Core entre-eux mais  également

les cache L2 séparés et même l'extérieur (à l'exception de la

mémoire Ram qui est directement reliée au processeur et pas par

l'intermédiaire du chipset. Intel avec l'I5 et l'I7

utilisent une structure tout à fait identique. Par contre, les Phenom

d'AMD modifient un peu cette architecture en reprenant en plus un cache

L3 partagé entre les différents coeurs.

également

les cache L2 séparés et même l'extérieur (à l'exception de la

mémoire Ram qui est directement reliée au processeur et pas par

l'intermédiaire du chipset. Intel avec l'I5 et l'I7

utilisent une structure tout à fait identique. Par contre, les Phenom

d'AMD modifient un peu cette architecture en reprenant en plus un cache

L3 partagé entre les différents coeurs.

5. L'architecture, source de performances?

Oui, c'est actuellement elle qui différencie les modèles et plus la fréquence pure de fonctionnement. Cette modification de structure a par exemple permit à Intel de diviser quasiment par 3 la fréquence lors du passage du Pentium IV à l'Intel Core. C'est également ce qui avait permis à AMD d'être plus performant avec ses premiers Athlon (à la même fréquence) par rapport aux Pentium III. Plus proche de nous, l'I7 avec une structure complètement remanié par rapport à ses prédécesseurs reste le plus performant actuellement à vitesse égale (et ce n'est pas que par l'utilisation de mémoires DDR3 ou DDR4).

|

8.2. Microprocesseur Intel actuels: P4, Intel Core, I5 et I7 - 8.3. Les microprocesseurs AMD: Athlon 64 et Phenom - 8.exercice. Remplacer un processeur utilisant un socket LPGA775 > 9. Les mémoires DDR, DDR2 et DDR3 Formationx41-> 7. Quelques composants en électronique: diodes, transistors, condensateurs, circuits intégrés, ... Dans le dictionnaire: architecture RISC - architecture CISC |

La formation X41-tech -> 1. Bases techniques en informatique -> Les processeurs pour PC -> Microprocesseurs AMD